|

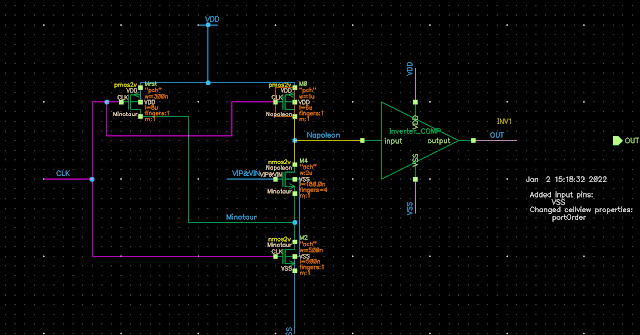

| 目前遇到電壓小一點點,電路無法產省正常的波形 |

解決方法:

我發現電壓如果寫VDD/2-dv 這樣的算法,好像輸出就有問題,發現了 VDD/2-VDD/2^12 ,這樣寫法會讓給的電壓有問題 ,只要寫次方項就有問題,改成VDD/4096

|

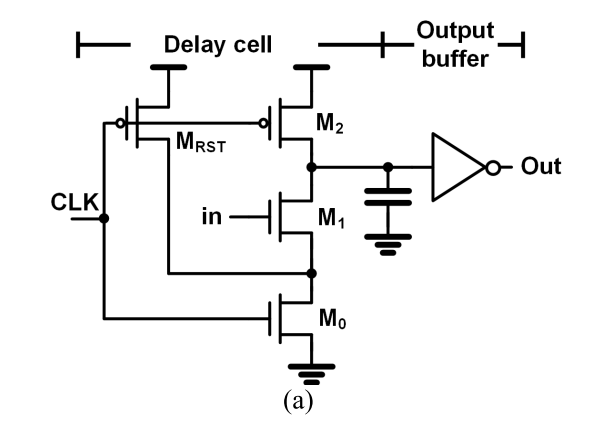

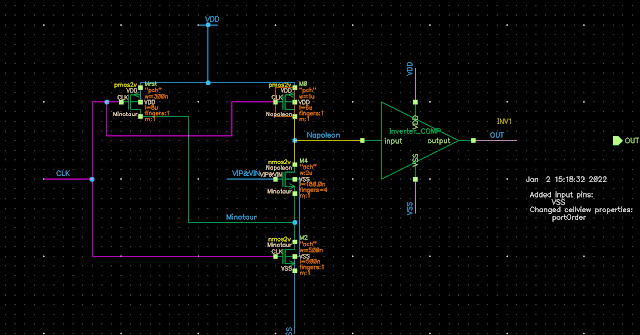

| Mintour的電壓變化,對Napoleon的電壓變化影響小 ,有可能是跟M4 mos 的size有關 |

|

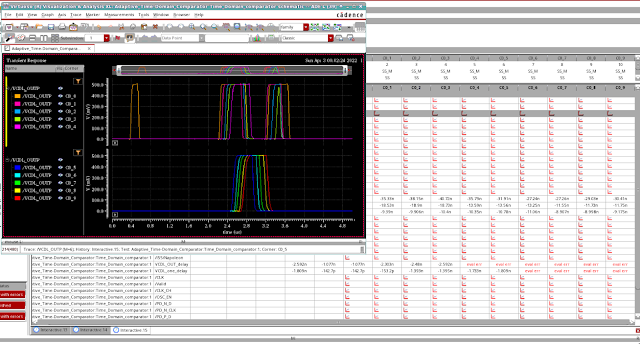

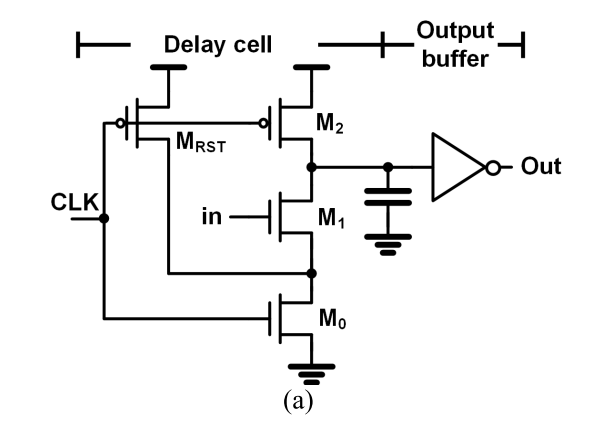

| 第三個VCDL 產生不出脈衝波的原因 |

|

| more detail about the three VCDL |

|

| 最早可以讓SS corner 可以work的 參數 |

|

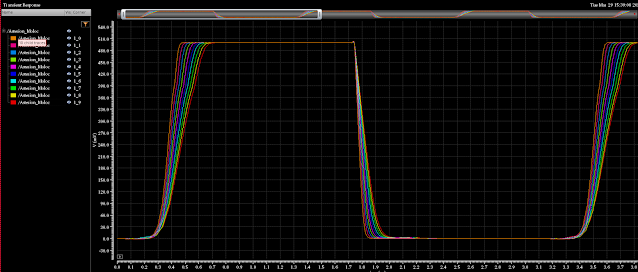

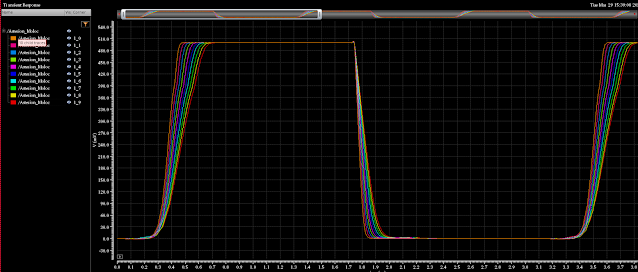

| SCAN M0 to gain the variation |

|

| SS corner situation , Ya my guess is right , but this is for VCDL tests alone |

|

| SCAN Mrst to gain the variation |

|

SS corner situation , Ya my guess is right , but this is for VCDL tests alone

|

---------------------------------------------------------------------------------------------------------------------------

當電路在DATA放 inverter 出來結果會相反

|

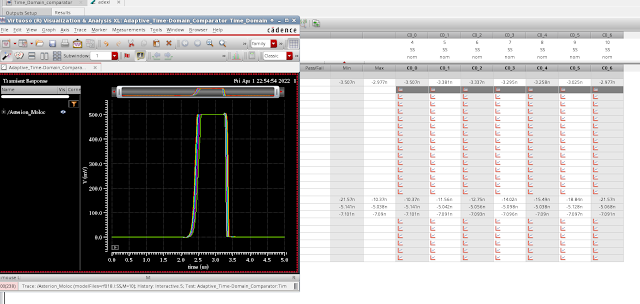

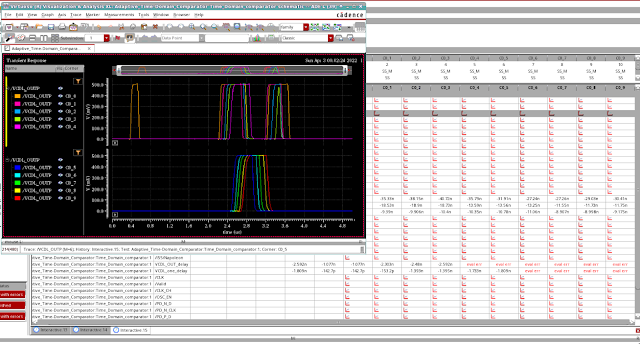

| 上面屬於PD_N 的數字 下面是屬於PD_P |

|

| VCDL array 如果這樣皆是不會起振,不管你是偶數級還是奇數級 |

|

| 這樣會有收斂問題 ,還是不能跑 ,但把Vctrlp Vctrln 電壓條好後就可以跑了 |

看起來有沒有加DTW 不影響 VCDL的輸出頻率 , 只有震盪次數的問題

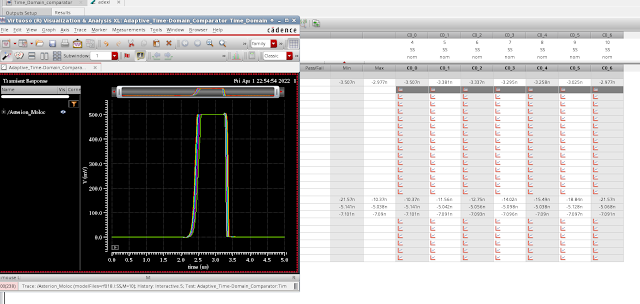

Time Domain Camparator 兩種狀況 右邊輸出預設為11才會運作出來

目目前使用的 目目前使用的 |

| SR -Latch 使用nor Gate |

|

當Vip > Vin

DTWP=1 , DTWN=0

Outp=1 Outn=0 |

|

當Vip < Vin

DTWP=0 , DTWN=1

Outp=0 Outn=1 |

|

SS corner 隨著電容增加 ,電壓脈衝波越來越難升上去

|

|

| 電容增大SS corner , dekay 時間基本上會增加 |

|

| Cap 增加 上升速度越慢 SS corner |

|

| M0 PMOS length 逐漸增加 ,上升速度越慢 ,Delay越長 |

|

| Length 越大 ,充電速度越慢 , X Pmos |

|

| 可以看到輸入mos 隨著mos增大 ,delay時間降低 ,上升速度越快 ,但變化不大 ,SS corner |

|

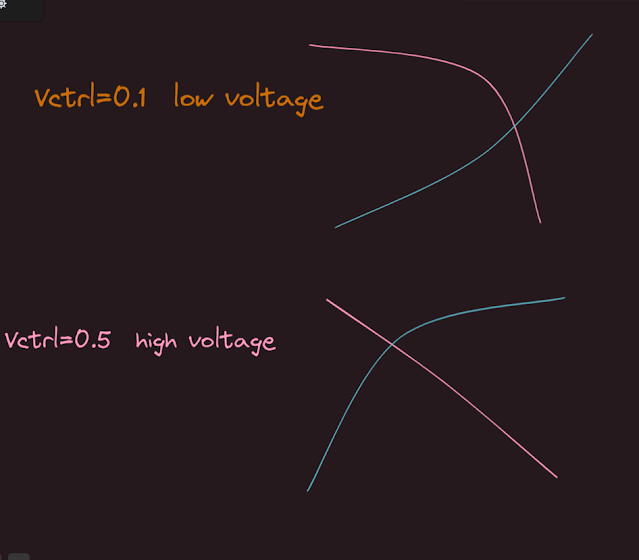

| 掃描VCDL 輸入Vip 的 Mos , 可以看到電壓越大 , delay 時間越小 , 上升速度越快 |

|

| VCDL mos輸入端 隨著mos增大 |

|

| 當Vctrl_n 電壓太小 ,會產生不出CLK ,根本就無法進行比較 |

|

| 你可以看到我已經在DTW 雙端控制電壓Vctrlp &Vctrln都用0.5V ,但脈衝波速度仍然有差可見寄生電容不一樣 |

|

| 條VCDL M0 pmos 的M ,M越大 充電速度越慢 ,分配的時間越少 ,震盪次數減少 |

|

| 可以知道M0 Pmos 如果width Finger越大 充電速度也是越慢 |

|

| 條M0 PMOS 的 Length 會導致放電速度變慢 ,差異非常大 |

|

| Mrst 掃描 M只有影響放電速度 當width增加,放電時間變慢而已 |

|

| Length增加 放電速度變慢 |

|

| Data那邊掃描Cap, 的掃描圖 |

|

| 當 Vip 電壓大於 Vin 時 的狀況 |

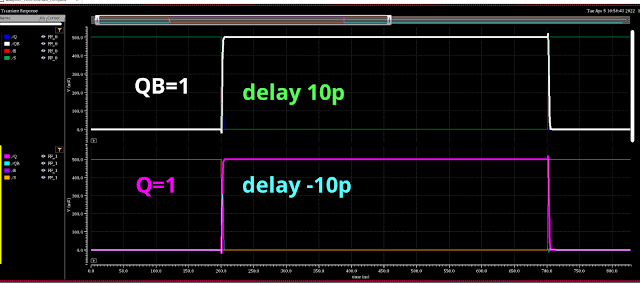

SR Latch

|

| S=1 R=0 --> Q=1 ,QB=0 |

|

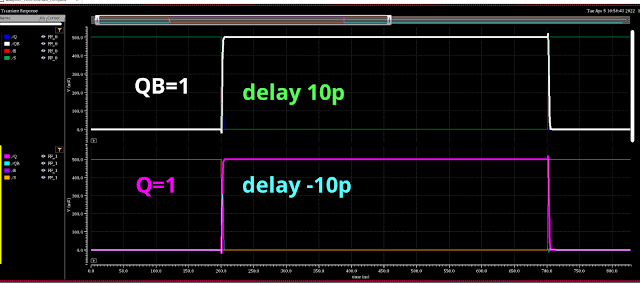

| 同樣狀況 , FS SS corner Q上升更慢 |

|

S=0 R=1 --> Q=0 ,QB=1

|

|

S=1 R=0 --> Q=1 ,QB=0

真的時間差到1n SR latch 會比錯 ,應該是要Q 跳起來 |

|

SR latch delay 10n , S=1 R=0 --> Q=1 ,QB=0 ,感覺Q 充電需要時間,不能被其他打斷

|

SR Latch 10p delay function work

|

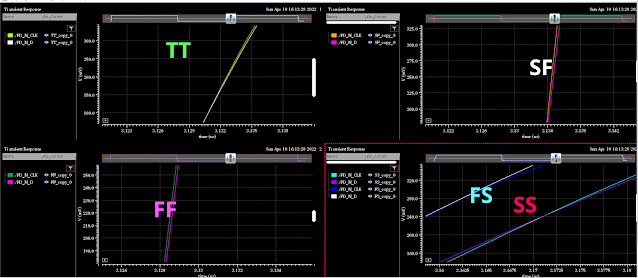

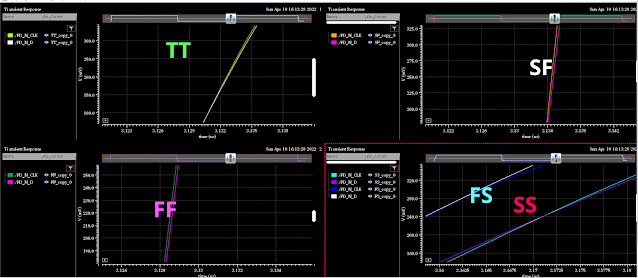

| TT |

|

| FF |

|

| SS |

|

| SF |

|

| FS |

|

| Pmos size 小 ,充電電流不夠 |

|

| 掃描仍然不行 ,已經把PMOS length 改成0.18u ,掃描M=10-30 ,仍然運作不了 |

|

| 拿掉DTW輸出電容。會讓DTW運作不了 |

|

| TPSC 條的差異 |

|

| pd_n_clk +pd_n_d= n寄生電容 , pd_p_clk+pd_p_d= p寄生電容 |

|

| 隨著dummy增加 ,確實時間差距越來越接近 |

|

| VCDL 上下參數都一樣狀態下 , 最終DTW 的結果 |

|

| TSPC_with_set_Original every corner 目前調出來 |

|

| TSPC_with_set_Original every corner Wave |

|

| 第二種TSPC_with_set 的delay時間 |

|

| TSPC_with_set evey wave |

|

| 目前電路調整的方向及邏輯 |

|

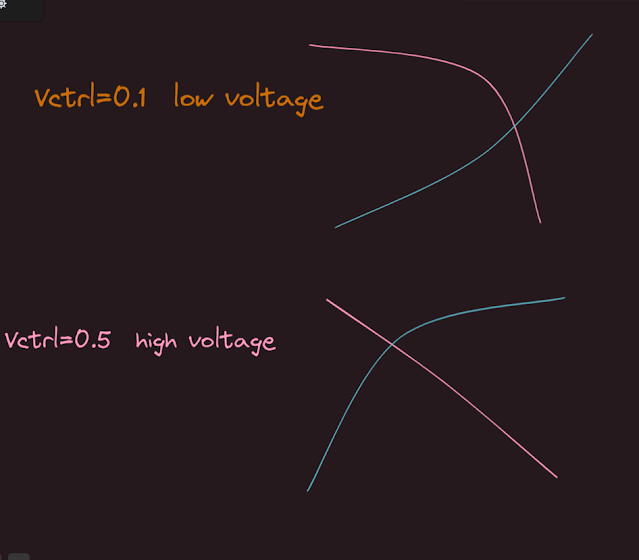

| 不同的Voltage control |

|

| 想辦法讓SS corner 充電速度變快 |

|

| 發現VCDL 每一級stage 的時間沒有成比例的增加 |

|

| FS corner 由 1u -1m 都沒什麼變化 ,很有問題 ,要調一下,試看看 |

|

| 掃描M7 finger=1~20 , 最佳解為finger=3 |

|

| 發現SS corner -25 -15 時無法運作 |

|

| FS corner input referred noise 5m , DOUT 也只有647.058mV ,超奇怪的 |

|

| VCDL M=3-9 TT corner |

|

| VCDL M=1-10 FF corner |

|

| VCDL Length=0.3u-2u , Length=2u 可以變為0.82mV |

|

| VCDL SS 4個 VCDL 脈衝波 , mench 感覺5個以上VCDL ,波就時間來不急 |

|

| normal nmos SS corner M=1-10 |

|

| 但不會成功運作 |

|

| TT corner 運作速度太快, DFF 來不及充放電,造成沒有如期運作 |

|

| Function ERROR |

目目前使用的

目目前使用的

留言

張貼留言