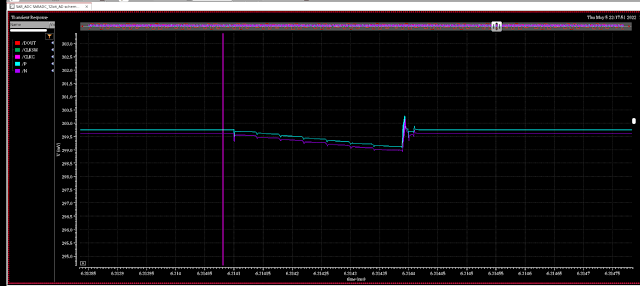

P & N 的電壓 , 一直處在SF corner放電 , 不知道是否會電壓產生影響 可以work的VCDL 以這個為標準 FF corner I discovered that Valid rise to slow , lead to VCDL still work , beciuse FF corner function speed is more quicklier , so compare to or gate , or gate charge speed is too slow , 完整的FF corner 在 Time Domain ADC 運作的問題點 發現到SS corner 在電壓差到10u 的狀況下 ,會剛好運作失敗 , 導致比較錯誤 FS corner 遇到 VCDL開始運作時 , kickbakc noise 產生Vip Vin 的大小順序相反的問題 理論上 ,用來跟上面錯誤突來對照 Vip > Vin 理論上應該是OP比較大 ,但比出來是ON比較大 ,在SS corner